플립 플롭 및 메모리 동작 이해

●NOR 게이트 2개를 조합하여 만들 수 있다

● flip-flop(플립플롭): 데이터를 저장하는 조합 논리 회로

○ 최초의 스위치를 누르면 점등하고, 스위치를 꺼도 점등한 채로 됩니다.

○ 두 번째 스위치를 끄면 불이 꺼지고 스위치를 끄더라도 사라진 상태로 유지됩니다.

● 스위치를 열고 닫을 수 있습니다.

○ 켜짐: 최근 첫 번째 회전 스위치가 켜졌습니다.

○ 불이 사라졌습니다: 최근 두 번째 스위치가 켜져 있습니다.

※전기를 앞에 넣었다는 사실을 기억할 수 있게 되었다

●RS플립플롭

○ Q는 output, Q ‘는 Q의 역값

○ 단, S와 R이 1인 상태는 피하도록 설계(Q와 Q’가 양쪽 모두 0이 되기 때문에)

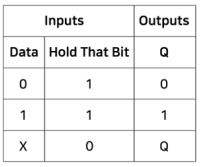

● Level -triggered flip-flop

○ RS 프리플롭에 Hold That Bit이라는 이름으로 조합 논리 회로 추가

○ Hold That Bit이 1인 경우에만 Data가 1일 때 출력값에 적용

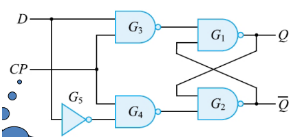

●D타입 플립플롭

○ R/S머리(input)를 Data(1개의 input)로 바꾸기

○ R/S 양쪽 모두 1 의 경우는 피하도록 설계하기로 한다

○ R / S 모두 0이면 Q 값에 영향을주지 않으므로 삭제

● Level-triggered D-type flip-flop

○ D 플립 플롭에 트리거 설치

○D는 데이터를 의미

○ Level-triggered는 Hold That Bit이 1인 경우에만 Data 값을 저장한다는 의미

○RS플립플롭으로 R/S 모두 1, 0의 경우를 피하도록 설계한 조합 논리회로

8×1 메모리 동작 및 구성 이해

● 1비트 래치

○ level-triggered D-type flip-flop

○ Data In이 데이터를 넣을 때 Write도 1이 되어야 합니다.

○1bit를 일시적으로 저장할 수 있는 메모리

●8비트 래치

○ Write가 1이면 8bit Data Inputs가 8bit Data Outputs에 저장됩니다.

○ Write가 0이면 8bit Data Outputs 값이 유지됩니다.

●8-to-1 셀렉터

○8비트 데이터로부터 특정 비트값만 출력

○ 8개의 1bit 래치 중에서 1개의 데이터 출력 신호를 선택할 수 있다

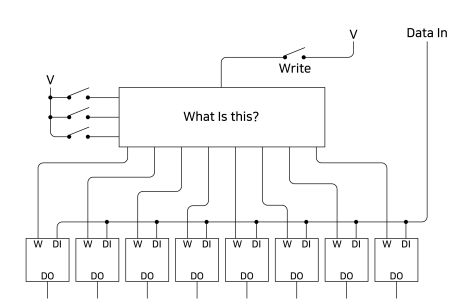

●3-to-8 디코더

○ 8개의 출력 중 V 스위치로 1개의 출력 이외에는 0

○Write가 1, V스위치로 특정의 출력을 선정, Data In의 값이 특정의 latch에 기입된다

● 완전한 8비트 래치 회로

○3-to-8 디코더와 8-to-1 셀렉터로 구성(address)

○S0, S1, S2가 디코더와 셀렉터에 동일하게 적용(데이터를 읽고 쓸 수 있는 주소)

○ Write가 1이면 Address에 Data In 값이 기록됩니다.

○ Data Out은 항상 Address에 해당하는 값을 출력합니다.

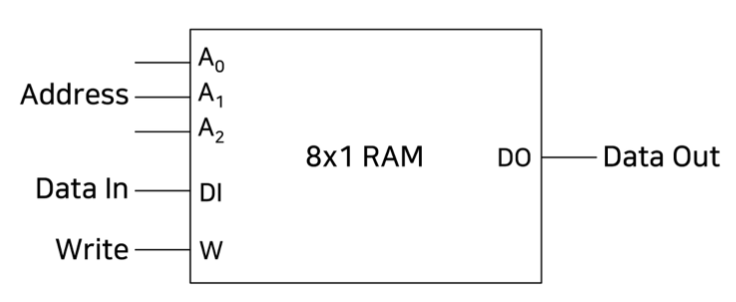

● RAM(Random Access Memory)

○ 완전한 8비트 래치 회로가 RAM

○3-to-8 디코더와 8-to-1 셀렉터로 구성

○ 3 Address가 있으면 8개 중 1개의 비트를 선택하여 쓰거나 읽을 수 있다

●8×1 RAM

○ 8비트 중 하나의 특정 비트를 쓰고 읽을 수 있는 메모리

○ Memory: 데이터 저장 가능

○ Read/Write: 특정 공간에 새로운 데이터를 저장, 읽기 가능

○ Random Access: Address 지정에 의해 특정 공간값 액세스 가능, 한편, 어느 메모리는 순차 액세스만 가능

64K 메모리 동작 및 구성 이해

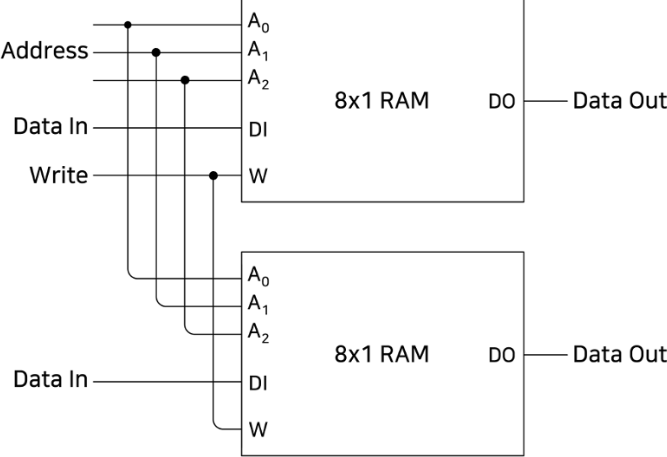

● RAM 어레이

○8×1 RAM을 2개 뜨개질

○Dara In은 각 8×1 RAM에 개별적으로 입력이 들어간다

○ Address와 Write는 2개의 8×1 RAM에 동일하게 입력이 들어간다

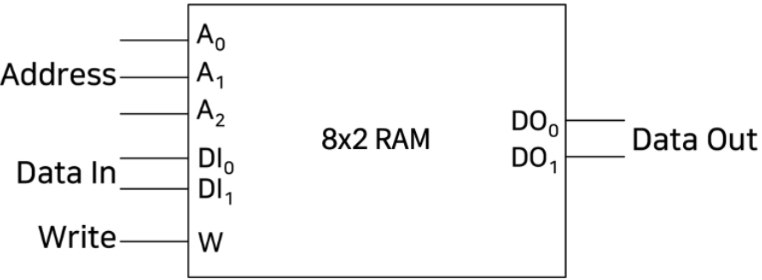

●8×2 RAM 어레이

○ 8개의 데이터를 저장하고 읽지만 각 데이터는 2비트

●16×1 RAM 어레이

○ 8 X 2 RAM 어레이 구조에 Select 및 1‑to‑2 Decoder/2‑to‑1 Selector 추가

○ 즉, Select는 네 번째 주소 역할을 합니다.

○ 16 개의 데이터를 저장하고 읽지만 각 데이터는 1 비트입니다.

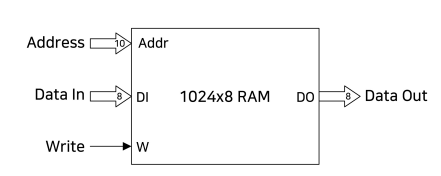

●m*n RAM array

○ 대량의 데이터를 저장하는 RAM 어레이 생성

○ 8 X 1 RAM을 복수 접속해, 복수의 Select로 Decoder/Selector를 구성하면, 많은 데이터를 읽어들여, 저장할 수 있다

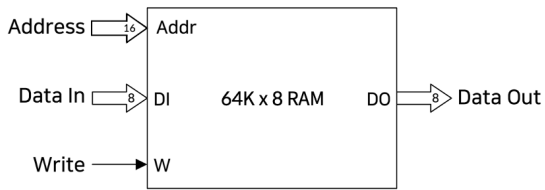

● 64K RAM

○ Address 수 / Data In / Out 수로 RAM 어레이 생성

○ 65,536(2의 16승) X 8 bits

○2의 16승 ――>16은 2 bytes, byte 단위가 편하기 때문에

Accumulator의 동작 및 구성 이해

● 클리어가 1인 경우 Q출력은 0이 됩니다.

● Flip-flop 값을 삭제할 수 있습니다.

● 데이터에 어떤 입력이 있어도 클리어 입력으로 출력값 삭제

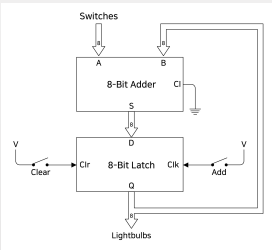

●8-Bit Adder와 8-Bit Latch로 구성

○클리어 스위치는 클리어 입력에 들어간다

○ Add 스위치는 Clock 입력으로 들어갑니다.

○ 8-bit Adder로 가산이 계산되고 이 값이 8-bit latch에 들어가려면 Add 스위치를 누르면 8-bit latch에 저장된다.

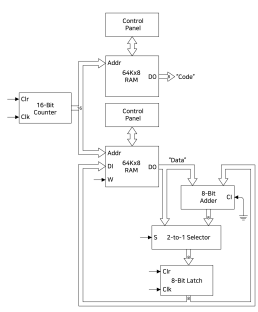

디지털 컴퓨터 및 프로그래밍 정보

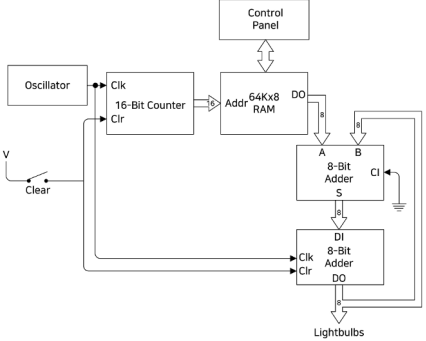

● Program Counter (PC)

○ 16-Bit Counter: 1씩 증가하는 조합 논리 회로

● 여러 숫자를 추가하고 싶을 때

○ 각 숫자를 0000h부터 순차적으로 씁니다.

Control Panel에서 Takeover 스위치를 1로 설정 한 후 각 숫자를 각 주소에 씁니다.

○ Takeover 스위치를 0으로 설정하여 더 이상 Control Panel이 RAM을 제어하지 않도록 합니다.

○ PC의 Clear 스위치가 0이 되면 PC는 0000h에서 RAM에서 데이터를 가져옵니다.

○ Adder가 값을 더합니다.

○ 클럭(Oscillator)이 0과 1로 바뀔 때마다 PC 값이 증가합니다.

● 자동화

○ 000h 주소에서 데이터가 저장됨

○ 세 개를 더하고 두 개를 더하고 세 개를 더한다고 가정합니다.

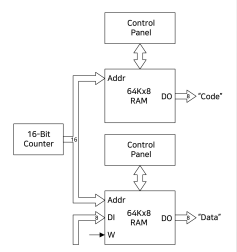

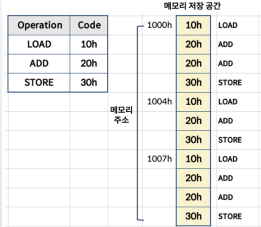

● Programming

○ 각 주소에 대응하여 Load, Add, Store를 의미하는 값을 작성해야 한다.

○ RAM을 분리하고 명령을 의미하는 값을 순차적으로 넣으면 코드를 실행할 수 있습니다.

○h는 Hex(16진수)를 의미

○ 이하와 같이 각 명령을 의미하는 숫자를 작성해, 각 주소에 맞는 코드를 넣는다

○ 명령 번호: Instruction Code, Operation Code 또는 opcode

● Load 및 Store 명령

○ Load: 2-to-1 Selector로 Data를 Add하지 않고 즉시 8-bit Latch에 넣기

○스토어: 8비트 래치 출력을 64Kx8 RAM에 즉시 저장(Write 스위치를 1로 설정)

레지스터 및 프로그래밍 정보

● Instruction Set 및 코드

○ 소프트웨어: 코드 + 데이터

○ 소프트웨어 엔지니어: 코드를 작성하는 사람

○ Machine language : CPU는 Instruction code를 작성하고 제공합니다.

○ 컴파일: 프로그래밍 언어로 작성된 프로그램은 컴파일러를 통해 CPU가 제공하는 Instruction code를 기반으로 변환됩니다.

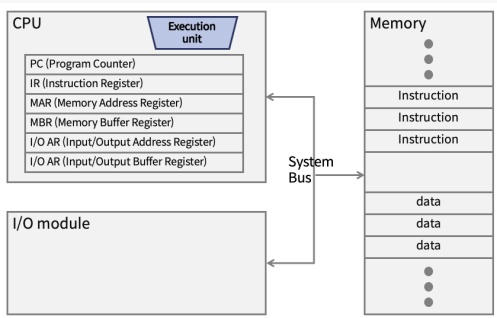

● 컴퓨터의 CPU 기본 구조

○ CPU에 레지스터라는 저장 공간이 있습니다.

빠른 실행

○ PC(Program Counter): 다음에 실행할 명령어 주소를 가리키는 레지스터

○ IR (Instruction Register) : 최신 페치 된 명령 아카이브 레지스터

○ 어큐뮬레이터(ACC, Accumulator): 데이터 임시 저장 레지스터

○ MAR (Memory Address Register) : CPU가 메모리 참조 용으로 유지하는 데이터 주소가있는 레지스터

○MBR(Memory Buffer Register): CPU가 메모리에서 읽거나 저장하는 데이터 자체를 저장하는 레지스터

CPU 파이프라인 정보

● 현재 컴퓨터의 CPU 기본 실행 구조

○ Instruction Fetch : 실행할 명령을 메모리에서 읽고 CPU로 가져옵니다.

– PC가 가리키는 주소를 MAR로 보내기

– MAR에 기록된 주소를 메모리에서 읽고 MBR로 전송

– MBR의 명령을 IR에 저장

– 다음 명령을 가리키도록 PC는 주소 값 증가

○ Instruction Decode: 페치된 명령어에 포함된 데이터 가져오기 및 명령어 디코딩

○ Instruction Execution: 명령 실행

– MBR 데이터와 ACC(Accumulator) 데이터로 연산 후 ACC(Accumulator)에 저장

○ Write Back: 실행 결과 저장

●현재 컴퓨터의 CPU 명령 구조

○ CPU마다 방식은 조금씩 다를 수 있지만, 기본적으로 하나의 명령은 opcode + argument(operand) 구조를 가질 수 있다

○ 3E는 사전에 약속된 load 명령, 이 때 바로 계속되는 데이터는 operand

○ load 명령에서 operand는 데이터가 있는 주소입니다.

○ 따라서 operand 주소에서 데이터를 검색하고 약속 된 레지스터에 저장

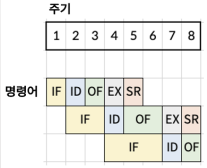

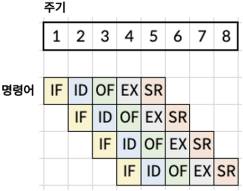

● CPU 성능을 향상시키는 기술 – 파이프라인

○ 파이프라인: 한 작업에 필요한 사항을 세부적으로 나누어 동시에 다른 세부 작업을 수행하는 기술

○ Fetch Stage (Instruction Fetch/Decode)

○ Execution Stage (Instruction Execution)

○명령 서랍(IF:Instruction Fetch)

○명령 해독(ID:Instruction Decode): 인출된 명령 해석

○ 오퍼랜드 페치(OF:Operand Fetch): 메모리로부터 데이터를 페치

○명령 실행(EX:Execute)

○실행 결과 저장(SR:STore)

CISC, RISC CPU 이해 및 컴퓨터 구조 정리

● CISC의 특성

○명령의 포맷이나 길이에 관한 규칙이 없다

○ 하나 이상의 사이클로 명령 (상세 작업) 실행

○ 모든 명령이 얼마나 걸리는지 시간 예측이 어렵습니다.

●RISC의 특성

○명령의 포맷과 길이 고정

○ 하나의 사이클로 명령 (상세 작업) 실행

○ 모든 지령 시간 예측 가능

● CISC/RISC CPU

○ 대표적인 CISC CPU: 인텔 CPU

○ 대표적인 RISC CPU: ARM/스마트폰, 임베디드, IoT 기기

● 메모리

○ 메모리가 높고 성능을 높이기 위한 전략

○비싼 메모리는 CPU의 바로 옆에, 짧게

○ 느린 메모리는 먼 곳에 그냥 크다.

○ 등록 : CPU 내에서 데이터 저장

○SRAM: L1, L2, L3 캐시

– 최대한 많이 사용하는 메모리의 데이터를 넣어 메모리까지 액세스하지 않고 CPU가 읽을 수 있도록 한다

○ DRAM: 메모리

○SSD/HDD(하드 디스크):PC의 전원을 꺼도 데이터를 보존

●DMA(Direct Memory Access)

○ CPU가 캐시까지는 데이터를 취득하는데 관여하지만 (Instruction Fetch)

○ 메모리, SSD로부터 데이터를 취득할 때까지 관여하면 CPU 활용도가 낮아진다

– DMA로 하고 메모리, SSD로 데이터를 관리하면 CPU는 이 시간을 명령 실행에 더 쓸 수 있다

● IO Devices

○ Input/Output Devices

– CDROM, 마우스, 키보드

– 프린터

– 네트워크 카드

○ 버스를 통해 IO 디바이스로 데이터 송수신